세계 주요 반도체업체들이 현미경으로나 겨우 볼 수 있는 나노입자의 셀 공간을 넓게 쓰는 첨단기술 개발에 박차를 가하고 있다.

반도체에서 셀은 반도체로서의 기능을 하는 최소 저장공간의 단위를 말한다. 이 메모리 셀이 모여 메모리코어(‘0’이나 ‘1’등의 정보를 저장하는 메모리 셀들이 모인 부분)를 형성한다.

지금까지 반도체업계는 이 메모리 셀의 크기를 줄이는 방식으로 대용량화를 실현해 왔다. 셀의 크기를 줄이는 방식은 2가지로 하나는 더 가는 미세가공기술을 적용하는 것(00나노 미세공정)과 셀 자체의 크기를 줄이는(0F스퀘어) 것이 그것이다.

하지만 최근들어서는 메모리 셀의 공간을 2분의 1, 3분의 1, 4분의 1 등으로 나누어 한 셀 당 저장용량을 2배·3배·4배 늘리는 기술에 관심이 모아지고 있다.

멀티레벨셀(MLC)이라고 불리는 셀 세분화 기술은 트랜지스터의 게이트를 다수의 전압 레벨로 변화시켜 셀 하나에 다수의 비트를 저장하는 기술이다.

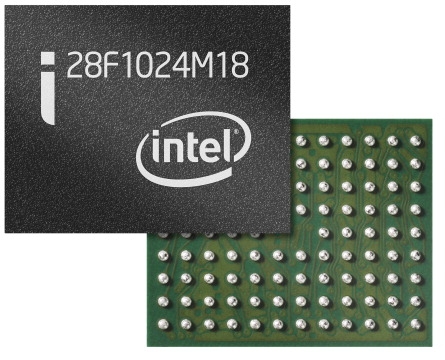

삼성전자·하이닉스반도체·인텔·스팬션 등이 치열한 기술개발 경쟁을 벌이고 있다. 현재 개발되고 있는 최대 용량 실현기술인 4비트 MLC(한 셀을 4등분)는 이론적으로 같은 공정에서 4배 용량의 메모리를 실현할 수 있어, 미세공정화와 더불어 메모리용량 확대의 핵심 기술로 평가받고 있다. 현재는 개발 공정이 단순한 플래시메모리분야를 중심으로 현실화되고 있다. 아직까지는 플래시메모리분야에 머물고 있지만, 향후 차세대메모리 제품들에도 응용될 가능성이 있다.

전문가들은 40나노 이하부터는 공정을 더 미세화하기보다는 다비트셀이 효과적일 것으로 보고 있다. 2비트를 넘어 3비트·4비트를 한 개 셀에 저장하면 공정을 한 단계더 미세화하는 것에 비해, 원가부담을 줄이는 효과가 크다는 판단 때문이다. 국내 주요 메모리업체가 내부적으로 검토하고 있는 자료에 따르면 ×3·×4 셀 제품은 40나노 공정에서 내년부터 본격적으로 시장을 형성해, 30나노급이 주류를 이룰 2009년 이후에는 시장 저변이 한층 넓어질 것으로 예상된다.

매년 미세 나노공정이 한 단계씩 줄어드는 것과 병행해 한 셀당 비트 수를 2배·3배·4배 늘리는 기술이 정착되면, 메모리 대용량화는 한층 가속화될 것이 분명하다. 실제로 삼성전자는 SLC를 중심으로 회로선폭을 줄여 두배씩 집적도를 높여왔으나, 8Gb에서 16Gb 낸드플래시로 넘어가던 2005년에는 제품 형태를 기존 SLC에서 2비트 MLC로 전환해 집적도 향상을 실현한 바 있다.

3비트와 4비트 셀은 아직은 신뢰성이 상용화의 걸림돌이다. 4비트 MLC는 대용량화측면에서 매우 긍정적이지만, 전하 누출과 관련된 신뢰성, 프로그램 공간 부족, 내구성에서 싱글레벨 셀에 비해 성능이 떨어진다. 따라서 MLC는 누가 먼저 양산을 시작하느냐만큼이나 누가 더 안정적인 기술 및 공정을 확보하느냐가 중요하다. 심규호기자@전자신문, khsim@